LP38512 PSOP 1.5A Fast-Transient Response LDO with Error Flag Evaluation Board

Texas Instruments

LP38512 PSOP 1.5A Fast-Transient Response LDO with Error Flag Evaluation Board

| Distributor | SKU | Stock | MOQ | 1 | 10 | 50 | 100 | 1,000 | 10,000 |

|---|---|---|---|---|---|---|---|---|---|

| DigiKey | LP38512MR-ADJEV/NOPB-ND | 0 | $53.90 | $53.90 | $53.90 | $53.90 | $53.90 | $53.90 | |

| Mouser Electronics | N/A | 0 |

TPS54620 8V to 17V; 6A SWIFT™ Converter Evaluation Module

Texas Instruments

TPS54620 8V to 17V; 6A SWIFT™ Converter Evaluation Module

| Distributor | SKU | Stock | MOQ | 1 | 10 | 50 | 100 | 1,000 | 10,000 |

|---|---|---|---|---|---|---|---|---|---|

| DigiKey | 296-24566-ND | 1 | $58.80 | $58.80 | $58.80 | $58.80 | $58.80 | $58.80 | |

| Arrow North American Components | TPS54620EVM-374 | 0 | 1 | $53.26 | $29.47 | $29.47 | $29.30 | $0.00 | $0.00 |

| AVNET Europe | TPS54620EVM-374 | 0 | 1 | * $38.08 | * $36.15 | * $32.85 | * $31.37 | * $31.37 | * $31.37 |

| AVNET Express | TPS54620EVM-374 | 0 | 1 | $30.50 | $30.50 | $30.50 | $30.50 | $30.50 | $30.50 |

| element14 APAC | TPS54620EVM-374 | 10 | 1 | * $70.33 | * $70.33 | * $70.33 | * $70.33 | * $70.33 | * $70.33 |

| Farnell | TPS54620EVM-374 | 16 | 1 | * $73.26 | * $73.26 | * $73.26 | * $73.26 | * $73.26 | * $73.26 |

| Mouser Electronics | 595-TPS54620EVM-374 | 7 | 1 | $63.71 | $63.71 | $63.71 | $63.71 | $63.71 | $63.71 |

| Newark | TPS54620EVM-374 | 1 | 1 | $65.43 | $63.89 | $63.89 | $63.89 | $63.89 | $63.89 |

| Texas Instruments | TPS54620EVM-374 | 20 | 1 | $49.00 | $49.00 | $49.00 | $49.00 | $49.00 | $49.00 |

| Verical Marketplace | TPS54620EVM-374 | 3 | 2 | $24.57 | $28.90 | $27.50 | $27.50 | $27.50 | $27.50 |

| Win Source | TPS54620EVM-374 | 570 | 1 |

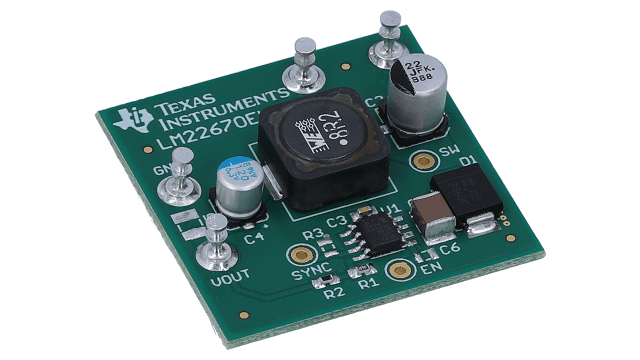

LM22670 3A SIMPLE SWITCHER regulator w/ Freq Adj or Synch and Precision Enable EVM

Texas Instruments

LM22670 3A SIMPLE SWITCHER regulator w/ Freq Adj or Synch and Precision Enable EVM

| Distributor | SKU | Stock | MOQ | 1 | 10 | 50 | 100 | 1,000 | 10,000 |

|---|---|---|---|---|---|---|---|---|---|

| DigiKey | LM22670EVAL-ND | 0 | $26.67 | $26.67 | $26.67 | $26.67 | $26.67 | $26.67 | |

| Mouser Electronics | 926-LM22670EVAL | 0 | 1 | ||||||

| Newark | LM22670EVAL | 0 | 1 | $0.00 | $0.00 | $0.00 | $0.00 | $0.00 | $0.00 |

DAC3282 Dual-Channel; 16-Bit; 625-MSPS; 1x-2x Interpolating Digital-to-Analog Evaluation Module

Texas Instruments

DAC3282 Dual-Channel; 16-Bit; 625-MSPS; 1x-2x Interpolating Digital-to-Analog Evaluation Module

| Distributor | SKU | Stock | MOQ | 1 | 10 | 50 | 100 | 1,000 | 10,000 |

|---|---|---|---|---|---|---|---|---|---|

| DigiKey | 296-30853-ND | 3 | $598.80 | $598.80 | $598.80 | $598.80 | $598.80 | $598.80 | |

| Arrow North American Components | DAC3282EVM | 0 | 1 | $575.77 | $596.35 | $596.35 | $583.56 | $578.82 | $506.16 |

| AVNET Express | DAC3282EVM | 0 | 1 | $608.78 | $608.78 | $608.78 | $608.78 | $608.78 | $608.78 |

| Mouser Electronics | 595-DAC3282EVM | 3 | 1 | $648.75 | $648.75 | $648.75 | $648.75 | $648.75 | $648.75 |

| Texas Instruments | DAC3282EVM | 4 | 1 | $499.00 | $499.00 | $499.00 | $499.00 | $499.00 | $499.00 |

| Verical Marketplace | DAC3282EVM | 14 | 1 | $702.82 | $665.33 | $665.33 | $665.33 | $665.33 | $665.33 |

| Distributor | SKU | Stock | MOQ | 1 | 10 | 50 | 100 | 1,000 | 10,000 |

|---|---|---|---|---|---|---|---|---|---|

| DigiKey | 296-18990-ND | 1 | $58.80 | $58.80 | $58.80 | $58.80 | $58.80 | $58.80 | |

| Arrow North American Components | TPS65100EVM-030 | 0 | 1 | $56.54 | $58.59 | $58.59 | $57.41 | $56.82 | $56.82 |

| AVNET Europe | TPS65100EVM-030 | 0 | 1 | * $67.07 | * $65.03 | * $61.39 | * $59.68 | * $59.68 | * $59.68 |

| AVNET Express | TPS65100EVM-030 | 0 | 1 | $59.78 | $59.78 | $59.78 | $59.78 | $59.78 | $59.78 |

| element14 APAC | TPS65100EVM-030 | 0 | 6 | * $0.00 | * $80.80 | * $80.80 | * $80.80 | * $80.80 | * $80.80 |

| Farnell | TPS65100EVM-030 | 0 | 6 | * $0.00 | * $58.74 | * $58.74 | * $58.74 | * $58.74 | * $58.74 |

| Mouser Electronics | 595-TPS65100EVM-030 | 4 | 1 | $63.71 | $63.71 | $63.71 | $63.71 | $63.71 | $63.71 |

| Newark | TPS65100EVM-030 | 0 | 6 | $50.73 | $50.73 | $50.73 | $50.73 | $50.73 | $50.73 |

| Texas Instruments | TPS65100EVM-030 | 13 | 1 | $49.00 | $49.00 | $49.00 | $49.00 | $49.00 | $49.00 |

| Verical Marketplace | TPS65100EVM-030 | 1 | 1 | $64.22 | $0.00 | $0.00 | $0.00 | $0.00 | $0.00 |

| Win Source | TPS65100EVM-030 | 10700 | 9 |

| Distributor | SKU | Stock | MOQ | 1 | 10 | 50 | 100 | 1,000 | 10,000 |

|---|---|---|---|---|---|---|---|---|---|

| DigiKey | 296-31297-ND | 0 | $532.75 | $532.75 | $532.75 | $532.75 | $532.75 | $532.75 | |

| AVNET Express | TRF2443EVM | 0 | 1 | $0.00 | $0.00 | $0.00 | $0.00 | $0.00 | $0.00 |

| element14 APAC | TRF2443EVM | 0 | 1 | * $613.63 | * $613.63 | * $613.63 | * $613.63 | * $613.63 | * $613.63 |

| Farnell | TRF2443EVM | 0 | * $674.18 | ||||||

| Mouser Electronics | 595-TRF2443EVM | 0 | 1 | $0.00 | |||||

| Newark | TRF2443EVM | 0 | 1 | $499.00 | $499.00 | $499.00 | $499.00 | $499.00 | $499.00 |

| Texas Instruments | TRF2443EVM | 13 | $499.00 |

| Distributor | SKU | Stock | MOQ | 1 | 10 | 50 | 100 | 1,000 | 10,000 |

|---|---|---|---|---|---|---|---|---|---|

| DigiKey | 296-20611-ND | 3 | $58.80 | $58.80 | $58.80 | $58.80 | $58.80 | $58.80 | |

| Arrow North American Components | TPS61045EVM-231 | 0 | 1 | $61.14 | $58.55 | $58.55 | $57.15 | $56.46 | $56.46 |

| AVNET Europe | TPS61045EVM-231 | 0 | 1 | * $67.07 | * $65.03 | * $61.39 | * $59.68 | * $59.68 | * $59.68 |

| AVNET Express | TPS61045EVM-231 | 0 | 1 | $59.78 | $59.78 | $59.78 | $59.78 | $59.78 | $59.78 |

| element14 APAC | TPS61045EVM-231 | 1 | 1 | * $80.16 | * $80.16 | * $80.16 | * $80.16 | * $80.16 | * $80.16 |

| Farnell | TPS61045EVM-231 | 1 | 1 | * $64.60 | * $64.60 | * $64.60 | * $64.60 | * $64.60 | * $64.60 |

| Mouser Electronics | 595-TPS61045EVM-231 | 2 | 1 | $63.71 | $63.71 | $63.71 | $63.71 | $63.71 | $63.71 |

| Newark | TPS61045EVM-231 | 1 | 6 | $20.93 | $20.93 | $20.93 | $20.93 | $20.93 | $20.93 |

| Texas Instruments | TPS61045EVM-231 | 16 | 1 | $49.00 | $49.00 | $49.00 | $49.00 | $49.00 | $49.00 |

| Verical Marketplace | TPS61045EVM-231 | 10 | 1 | $49.73 | $49.73 | $49.73 | $49.73 | $49.73 | $49.73 |

PHYTER® Industrial Temperature Single Port 10 100 Mbs Ethernet Physical Layer Transceiver

Texas Instruments

PHYTER® Industrial Temperature Single Port 10 100 Mbs Ethernet Physical Layer Transceiver

| Distributor | SKU | Stock | MOQ | 1 | 10 | 50 | 100 | 1,000 | 10,000 |

|---|---|---|---|---|---|---|---|---|---|

| DigiKey | DP83848I-MAU-EK-ND | 0 | $64.03 | $64.03 | $64.03 | $64.03 | $64.03 | $64.03 |

LM2833Z eMSOP - 3MHz 3.0A Step-Down DC-DC Switching Regulator Evaluation Module

Texas Instruments

LM2833Z eMSOP - 3MHz 3.0A Step-Down DC-DC Switching Regulator Evaluation Module

| Distributor | SKU | Stock | MOQ | 1 | 10 | 50 | 100 | 1,000 | 10,000 |

|---|---|---|---|---|---|---|---|---|---|

| DigiKey | LM2833ZMYEVAL-ND | 0 | $53.90 | $53.90 | $53.90 | $53.90 | $53.90 | $53.90 | |

| Arrow North American Components | LM2833ZMYEVAL | 0 | 1 | $0.00 | $50.68 | $50.68 | $50.39 | $49.70 | $49.70 |

| AVNET Express | LM2833ZMYEVAL | 0 | 1 | $0.00 | $0.00 | $0.00 | $0.00 | $0.00 | $0.00 |

| Mouser Electronics | 926-LM2833ZMYEVAL | 0 | 1 | ||||||

| Newark | LM2833ZMYEVAL | 0 | 1 | $50.73 | $50.73 | $50.73 | $50.73 | $50.73 | $50.73 |

| Texas Instruments | LM2833ZMYEVAL | 46 | 1 | $49.00 | $49.00 | $49.00 | $49.00 | $49.00 | $49.00 |

| Verical Marketplace | LM2833ZMYEVAL | 30 | 1 | $62.38 | $56.71 | $55.27 | $55.27 | $55.27 | $55.27 |

| Distributor | SKU | Stock | MOQ | 1 | 10 | 50 | 100 | 1,000 | 10,000 |

|---|---|---|---|---|---|---|---|---|---|

| DigiKey | LMH6518SQEVK/NOPB-ND | 0 | $311.25 | $311.25 | $311.25 | $311.25 | $311.25 | $311.25 | |

| Mouser Electronics | 926-LMH6518SQEVK | 0 | 1 |